- HubPages»

- Technology»

- Computers & Software»

- Computer Science & Programming»

- Programming Languages

Branching instruction and Processor control instruction

Branching Instruction

Op-code

| Operands

| Description

|

|---|---|---|

JMP

| 16 BIT MEMORY ADD/LABEL

| Jumps to given memory location or label

|

JC

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if CF=1

|

JNC

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if CF=0

|

JP

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if positive[SF=0]

|

JM

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if minus[SF=1]

|

JZ

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if ZERO[ZF=1]

|

JNZ

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if NOT ZERO[ZF=0]

|

JPE

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if EVEN PARITY[PF=1]

|

JPO

| 16 BIT MEMORY ADD/LABEL

| Jump to label/memory location if ODD PARITY[PF=0]

|

CALL

| 16 bit address

| Call unconditionally the subroutine

|

CC

| 16 bit address

| Call the subroutine if CF=1

|

CNC

| 16 bit address

| Call the subroutine if CF=0

|

CP

| 16 bit address

| Call the subroutine if SF=0

|

CM

| 16 bit address

| Call the subroutine if SF=1

|

CZ

| 16 bit address

| Call the subroutine if ZF=1

|

CNZ

| 16 bit address

| Call the subroutine if ZF=0

|

CPE

| 16 bit address

| Call the subroutine if PF=1

|

CPO

| 16 bit address

| Call the subroutine if PF=0

|

RET

| Return the program control from where Called

| |

RC

| Return if CF=1

| |

RNC

| Return if CF=0

| |

RP

| Return if SF=1

| |

RM

| Return if SF=0

| |

RZ

| Return if ZF=1

| |

RNZ

| Return if ZF=0

| |

RPE

| Return if PF=1

| |

RPO

| Return if PF=0

|

JMP: The instruction performs the unconditional jump. The program counter jumps to the location or label specified by the instruction.

For Example: JMP L1 // Jumps the program control to the label L1 in the program

Following are the conditional jump instructions:

JC: Jump to the label specified if the CF = 1. The isntruction checks the status of CF, and jumps if it is set to 1.

For Example: JC L2 // jumps to L2 label in the program if CF = 1 else go to next instruction.

JNC: Jump to the label specified if the CF = 0. The instruction checks the status of CF, and jumps if it is set to 0.

For Example: JC L3 // jumps to L3 label in the program if CF = 0 else go to next instruction.

JP: The instruction jumps the program control to the label specified if the result is positive (SF=0).

For Example: JP L4 // jumps to L4 if the SF = 0 else go to next instruction.

JM: The instruction jumps the program control to the label specified if the result is negative (SF=1).

For Example: JP L5 // jumps to L5 if the SF = 1 else go to next instruction.

JZ: The instruction jumps the program control to the label specified if the result is zero (ZF=1).

For Example: JP L6 // jumps to L6 if the ZF= 1 else go to next instruction.

JNZ: The instruction jumps the program control to the label specified if the result is non-zero (ZF=0).

For Example: JP L6 // jumps to L6 if the ZF= 0 else go to next instruction.

JPE: The instruction jumps if the even parity is set and PF = 1 else go to next instruction.

For example: JPE L7 // jumps if PF=1

JPO: The program control jumps to label specified if the PF= 0 i.e. the odd parity is set.

For Example: JPO L7 // jump if PF=0

Following instructions can be used for calling subroutine and returning from subroutine execution to main program.

CALL: The instruction calls the subroutine. The program control transfers to the address specified into the instruction. But before calling the subroutine, the next instruction address in program is stored into stack.

CC: The subroutine is called from current sequence of instruction execution if the CF = 1. Before calling the subroutine, the next instruction address from where the CC instruction executed is stored into the stack.

CNC: The subroutine is called from current sequence of instruction execution if the CF = 0. Before calling the subroutine, the next instruction address from where the CNC instruction executed is stored into the stack.

CP: The subroutine is called from current sequence of instruction execution if the SF = 0 [result is positive]. Before calling the subroutine, the next instruction address from where the CP instruction executed is stored into the stack.

CM: The subroutine is called from current sequence of instruction execution if the SF = 1 [result is negative]. Before calling the subroutine, the next instruction address from where the CM instruction executed is stored into the stack

CZ: The subroutine is called from current sequence of instruction execution if the ZF = 1 [result is zero]. Before calling the subroutine, the next instruction address from where the CZ instruction executed is stored into the stack.

CNZ: The subroutine is called from current sequence of instruction execution if the ZF= 0 [result is non-zero]. Before calling the subroutine, the next instruction address from where the CNZ instruction executed is stored into the stack

CPE: The instruction calls the subroutine if the PF = 1 [Even Parity]. Before calling subroutine, the address of next instruction is pushed into the stack.

CPO:The instruction calls the subroutine if the PF = 0 [Odd Parity]. Before calling subroutine, the address of next instruction is pushed into the stack.

RET: The instruction is the unconditional return instruction. When executed, it pop out the address from stack and transfers the program control back to old sequence from where the subroutine was called.

RC: The instruction is the conditional return instruction. Returns to the address at the top of stack if CF = 1.

RNC: The instruction is the conditional return instruction. Returns to the address at the top of stack if CF = 0.

RP: The instruction is the conditional return instruction. Returns to the address at the top of stack if SF = 0.

RM: The instruction is the conditional return instruction. Returns to the address at the top of stack if SF = 1.

RZ: The instruction is the conditional return instruction. Returns to the address at the top of stack if ZF = q.

RNZ: The instruction is the conditional return instruction. Returns to the address at the top of stack if ZF = 0.

RPE:The instruction is the conditional return instruction. Returns to the address at the top of stack if PF = 1.

RPO:The instruction is the conditional return instruction. Returns to the address at the top of stack if pF = 0.

Processor Control Instructions

Op-code

| Operands

| Description

|

|---|---|---|

RST

| 0 - 7 value

| Restart S/w Interrupt, calls specific interrupt subroutine

|

NOP

| No Operation

| |

HLT

| Halts the further execution

| |

DI

| Disable Interrupt

| |

EI

| Enable Interrupt

| |

RIM

| Read Interrupt mask

| |

SIM

| Set Interrupt mask

|

RST: The RST instruction calls the interrupt subroutine. There are 8 software interrupts numbered (0--7) are called when the instruction is executed. The following are the RST addresses:

- RST 0 0000h

- RST 1 0008h

- RST 2 0010h

- RST 3 0018h

- RST 4 0020h

- RST 5 0028h

- RST 6 0030h

- RST 7 0038h

NOP: The instruction performs No operation. The instruction is fetched, decoded and no operation is performed, hence we can say that it is used for utilizing some processor cycle. It is generally used for generating delay.

HLT: The HLT instruction indicates the halt in the execution of program. The processor waits for further execution. Generally the instruction is used to denote the end of program.

DI: Disable Interrupt. The instruction disables the mask-able interrupts while executing some important section of program.

EI: Enable Interrupt. The instruction enables the mask-able interrupt while executing the program.

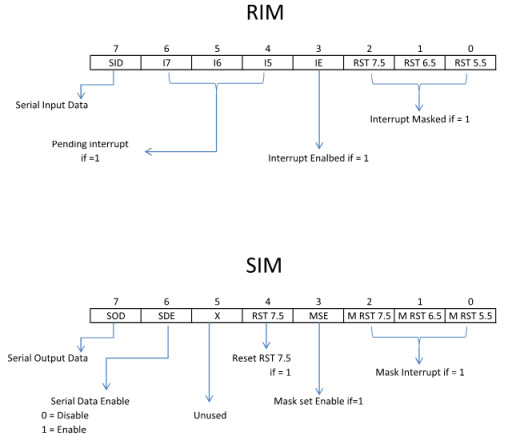

RIM: The instruction is used to read the status of RST 7.5, RST 6.5, RST 5.5 interrupt input lines. The status is stored into the accumulator.

SIM: The instruction stores the interrupt mask values for RST 7.5, RST 6.5, RST 5.5. The accumulator content is stored as the mask values. To set the interrupt mask the contents are pre-loaded into the accumulator.

Following figures shows the RIM and SIM status format:

How do you like the article?

Instruction Set of 8085

- INSTRUCTION SET OF 8085: Data Transfer Instruction

The 8085 microprocessor is programmed by assembly language programming. The article lists and explains Data Transfer instructions available in assembly language programming for 8085 microprocessor. - Arithmetic and Logical Instructions 8085

The 8085 microprocessor is programmed by assembly language programming. The article lists and explains Arithmetic and Logical instructions of assembly language programming for 8085 microprocessor.